|

| ||||||||||||||||||||

|

| |||||||||||||||||||||

Crypto Acceleration Using Asynchronous FPGAs

|

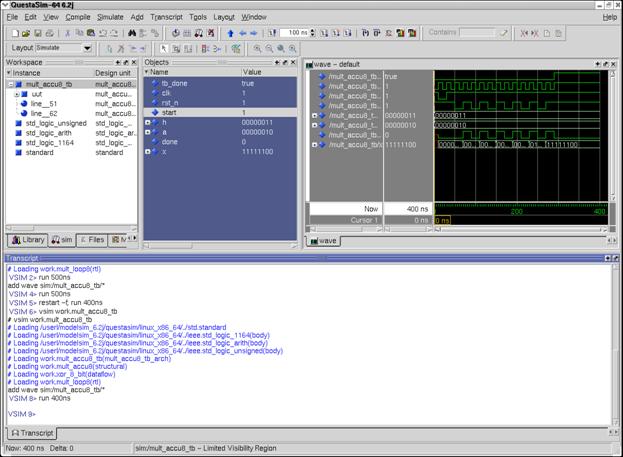

Introduction The goal of this project, sponsored by General Dynamics C4 Systems, is to evaluate proprietary FPGA technology developed by Achronix Semiconductor Corporation and its effectiveness using a 128-bit, one clock cycle multiplier in a finite field, GF(2 128 ), as a test application. The testing will determine if there is a significant increase in speed that can be achieved by simple modifications of existing synchronous HDL designs using three metrics: number of LUTs, number of registers, and clock speed Throughout the course of this project, multiple software tools were used in order to facilitate simulation, version comparison and simplification processes to increase productivity. The most important of these tools are explained in further detail in this section. Mentor Graphics QuestaSimQuesta is Mentor Graphics' Advanced Functional Verification (AFV) tool and is an integrated platform that includes QuestaSim. QuestaSim is capable of high efficiency advanced verification of large electronic systems, and includes built-in management and debugging utilities. QuestaSim, based upon Mentor Graphics' ModelSim, seen in Figure 1 , is a standards-based digital simulator capable of receiving VHDL or a variety of other languages' code as input and simulating results based on test bench waveforms.

QuestaSim displaying simulation results for a period of 400ns QuestaSim boasts a variety of features in addition to its primary functionality, such as low-power design verification and fast time-to-debug using assertions and a multi-abstraction debug environment [11]. Synplicity Synplify and Synplify Pro Synplify is synthesis engine that is used to create FPGA designs. It takes in VHDL or Verilog code and outputs a netlist which can be optimized for a variety of FPGA vendors and packages. Synplify uses Behavior Extracting Synthesis Technology® (B.E.S.T. T) to produce designs which are fast and highly efficient. Additionally, it is designed with a simple interface so that it is easy to use

Synplify Pro is similar in operation and use to that of Synplify, but offers better algorithms for compilation and mapping. In addition, it also improves the user interface (the Synplify Pro interface can be seen in Figure 3) and adds a great deal more options that may be used in design. This project uses both Synplify and Synplify Pro, the latter being used in situations concerning benchmarking due to the need of the auto constraining feature found within Synplify Pro. Achronix CAD Environment (ACE)The Achronix CAD Environment runs as a complementary tool to Synplicity's Synplify Pro software, seen in Figure 3 , and allows for enhanced optimization techniques using Achronix's proprietary technology to decrease routing delays. This results in an overall throughput increase of the system and allows for FPGAs to run some applications at speeds greater than 1GHz. ACE, which can be seen in Figure 4 , has been designed to be intentionally easy to use and while it functions on the premises of an asynchronous logic design, all input to the program is standard architecture, synchronous logic designs. This allows for current configurations to only require slight HDL modifications in order to benefit from the performance improvements ACE offers.

Altera's Quartus II software is a product of the Altera Corporation that provides a unified development design flow for FPGAs, structured ASICs, and CPLDs. Quartus II is capable of easily addressing problems relevant to designs such as post place-and-route design modifications. Compared to the Xilinx ISE, Quartus II provides higher benchmarks in performance with relevance to FPGA and CPLD designs. Quartus II also provides tools such as TimeQuest and PowerPlay that assist in timing analysis and power analysis, respectively, as well as a pin planner feature to be used in I/O pin assignment

Related Projects : Digital Diary Project,An Intelligent Eye,Secure Group Communication,Rich Internet Application for Weekly Automatic College Timetable, GenerationPortable Media Player,Low Cost Wireless Internet,Digital System Architecture,Bluetooth Project,XML-enabled Wrapper Construction,Empirical Model of HTTP Network Traffic,Query Processing in Global Information Systems,A Conceptual Graph Approach to Support Multiperspective, Development Environments,J3ME and Bluetooth Enabled Mobile Based Full Duplex Automation System,Image Steganography,Generic SQL Explorer,Face Detection Using Epitomic Analysis,Computer Troubleshooting Intelligent System,Customer Complaint Report Software,ER Diagram Maker,Dynamic Flash Interface,Device Switching Using PC’s Parallel Port,Design And Analysis Of Sense Amplifier,DEMOS Online Quiz,Insurance Database,Crypto Acceleration Using Asynchronous FPGAs,Congestion control in ATM-based Broadband ISDNs,Comparison Of Clustering Algorithms,Comparison & Simulation of Different Queuing Models,Collaboration Server,Implementation of Software Management and Maintenance,Bank Management System,Accelerating Ranking System Using Webgraph

<< back |

| All

rights reserved ® Copyright © V2computers 2007 through 2014 |